Engineering and Technology

Ultrashort vertical-channel MoS<sub>2</sub> transistor using a self-aligned contact

L. Liu, Y. Chen, et al.

Two-dimensional semiconductors are promising channel materials for highly scaled transistors because their atomically thin, dangling-bond-free surfaces enable aggressive body thickness scaling to mitigate short-channel effects and reduce power consumption. Prior demonstrations achieved ultrashort gate lengths in MoS2 transistors using a single-wall carbon nanotube (≈1 nm) and graphene (≈0.34 nm) as gates, showing good switching with low subthreshold swing and high on/off ratios. However, these approaches suffered from long channel lengths (typically ≥500 nm) due to challenges in aligning the source/drain electrodes with the ultrashort gate, severely limiting on-state current. The research question addressed here is whether a self-alignment process compatible with vertical device geometry can simultaneously scale gate length and channel length in 2D MoS2 transistors to unlock higher drive current while maintaining good electrostatic control. The study aims to develop a vertical self-aligned architecture that precisely aligns source/drain contacts to a graphene edge gate, with the channel length dictated solely by the heterostructure thickness, thereby overcoming lithographic and alignment constraints.

The work builds on extensive efforts to scale 2D transistors. SWCNT-gated MoS2 devices achieved ~1 nm gate length with SS ≈ 65 mV/dec and on/off ≈ 10^6 but retained ~500 nm channel length and ~30 μA/μm on-current due to alignment difficulties. Graphene edge-gated vertical MoS2 devices pushed gate length to ~0.34 nm with on/off >10^5, yet channel lengths again exceeded 500 nm and on-current was ~0.5 μA/μm, limited by misalignment between source/drain and side gate. Conventional CMOS self-alignment (gate-first masking) is not directly applicable: SWCNT gates have insufficient topography (~1 nm height), and vertical geometries are incompatible with lateral top-down self-alignment methods (evaporation through gate masks) that form structures only in-plane. Prior vertical 2D devices also struggled to conformally contact vertical sidewalls, often introducing strain, air gaps, and poor gate control. These limitations motivate a new self-alignment strategy tailored to vertical van der Waals heterostructures.

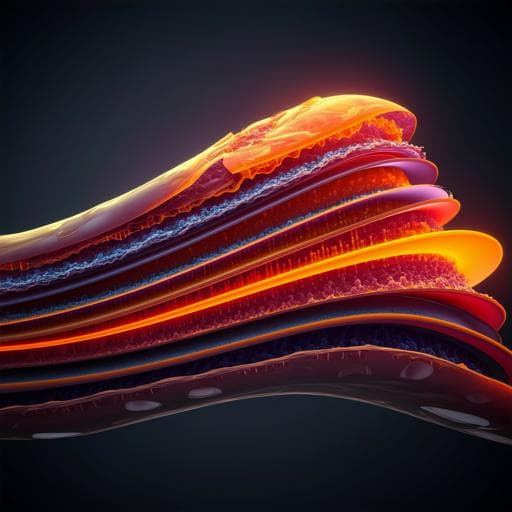

Device architecture: A folded vertical graphene/BN/MoS2 van der Waals heterostructure is used to realize a channel-all-around configuration with a lateral graphene gate wrapped by BN dielectric adjacent to a vertical MoS2 channel at the folded edge. Gate length is set by graphene thickness (~sub-1 nm) and the channel length is set by the folded stack thickness and curvature at the edge (~half of the perimeter of the fold).

Stacking and folding: A tri-layer MoS2/BN/graphene stack is assembled by dry alignment transfer under an optical microscope. In this stack, graphene is the gate, BN (5–20 nm) is the gate dielectric, and MoS2 (few layers, ~5–6 nm) is the channel. A custom PDMS pyramid tip (~5 μm apex) is fabricated via sequential droplet curing with progressively smaller tungsten needles and coated with PVC to enhance adhesion. The PDMS tip contacts one side/corner of the stack and is lifted vertically then moved laterally to mechanically fold the heterostructure, forming a folded fin where BN and MoS2 wrap around and conformally contact the graphene edge.

Self-aligned contacts: Ti/Au (5/25 nm) is evaporated atop the folded heterostructure to form a top contact. Leveraging weak adhesion between the heterostructure and the substrate, the metal above the heterostructure is mechanically peeled off while the metal on the SiO2 substrate remains (strong Ti–SiO2 adhesion), causing the top electrode to break precisely at the heterostructure edge and self-align to it without gaps or shorts. The peeled metal together with the folded heterostructure is then laminated onto an ultra-flat bottom Au electrode (30 nm) prepared by a metal flipping technique to ensure atomically smooth van der Waals contact. Final gate and source/drain pads are formed by evaporating Ti/Au (10/30 nm).

Post-processing and measurement: Devices are thermally annealed in Ar at 220 °C for 2 h to remove residues and improve contacts. Electrical measurements are performed at room temperature under vacuum (1.2 × 10^−6 torr), using the top metal as drain, bottom metal as grounded source, and the folded graphene as the side gate. The gate electrode (bilayer graphene in tested devices) is verified to have low resistance (~1.5 kΩ, two-terminal). TCAD simulations are used to examine carrier concentration distribution in the vertical channel under different gate biases.

Controls and variants: A control device fabricated without the self-alignment step uses standard lithography, leaving the drain ~0.7 μm from the heterostructure edge (typical e-beam limit), so the gate remains short but the channel is long. Thickness-dependent studies include thicker stacks (e.g., BN 50 nm, MoS2 5 nm, bilayer graphene) to probe strain and performance impacts and efforts to reduce total thickness below 30 nm to shorten channel length. Flexible devices are fabricated on polyimide (PI) substrates and tested under 5% strain. Additional process details include PDMS tip fabrication, heterostructure folding sequence, and the flipped bottom electrode formation using PPC support and high-temperature anneal to remove PPC.

- Simultaneous scaling achieved: Sub-1 nm gate length (graphene thickness) and sub-50 nm channel length were realized in a vertical MoS2 transistor via a folded, channel-all-around architecture. A representative device had Lch ≈ 47 nm (from a ~30 nm-thick folded stack).

- Performance of self-aligned device: n-type characteristics with on/off ratio ≈ 5 × 10^6 at Vds = 1 V, decreasing to ≈ 8 × 10^5 at Vds = 4 V; peak on-state current density ≈ 250 μA/μm at Vds = 4 V. Output characteristics show asymmetry consistent with different Schottky barriers at the bottom vdW Au (higher barrier to n-type MoS2) and top Ti contacts (lower barrier).

- Control (non-self-aligned) device: With ~0.7 μm separation from the heterostructure edge (long channel), the on-state current density is ≈ 6 μA/μm at Vds = 4 V—over 40× lower than the self-aligned device—demonstrating the benefit of self-aligned short channel.

- Yield and stability: Among 18 self-aligned devices, 14 functioned (≈77% yield). On/off ratios remain 10^6–10^7 down to Lch ≈ 47 nm, indicating good electrostatics with ultrathin 2D channels. Device characteristics were stable over 3 months in air.

- Thickness dependence and strain: Thicker stacks (>60 nm) introduce large tensile/compressive strain near the fold, causing structural distortions, air gaps, and flake breakage (TEM/EDS evidence). A thick device (BN 50 nm, MoS2 5 nm, bilayer graphene) shows n-type behavior with on/off >10^4, needs ~15 V to turn off (thicker BN), and delivers ~60 μA/μm at Vds = 4 V due to longer channel.

- Lower thickness limit: Attempts to reduce total thickness below ~30 nm face practical limits because metal thickness needed for conductivity approaches stack thickness, preventing reliable crack/peel self-alignment at the edge and leading to device failure.

- Flexible devices: On PI under 5% strain, transistors maintain function with on/off ≈ 10^1 at 10 mV and ≈ 10^2 at 4 V, and reach ~62 μA/μm at 4 V, indicating bending insensitivity of the vertical current path.

- Simulations: Carrier concentration is low at Vgs = −5 V (off) and concentrated near the tip region at Vgs = +5 V (on), consistent with channel-all-around gating.

- Theoretical scaling: Considering mechanical and leakage constraints (graphene ~0.3 nm, MoS2 ~4.5 nm, BN ~5 nm), pre-fold thickness ~10 nm could theoretically yield sub-30 nm channel length, but BN leakage and MoS2 mechanical fragility are limiting factors.

The study demonstrates that a folded, channel-all-around vertical architecture enables precise vertical self-alignment of source/drain contacts to an ultrathin graphene edge gate, addressing the long-standing challenge of simultaneously scaling gate and channel lengths in 2D MoS2 transistors. The self-alignment relies on controlled metal peeling at the heterostructure edge and a flipped ultra-flat bottom electrode to ensure intimate van der Waals contacts. The resulting devices show substantially higher on-state current than prior short-gate demonstrations and non-self-aligned controls while maintaining high on/off ratios, validating that channel length, not gate length alone, is critical to drive current in ultra-scaled 2D FETs. The asymmetric output behavior is consistent with contact barrier asymmetry and does not impede the main conclusion about current enhancement from channel scaling. The approach is compatible with flexible substrates and preserves performance under strain, highlighting the advantages of vertical current flow in flexible electronics. Overall, the results provide a path forward for ultra-scaled 2D transistors and vertical van der Waals devices that are incompatible with conventional lateral self-alignment techniques.

A self-aligned fabrication strategy based on folding a graphene/BN/MoS2 heterostructure realizes vertical MoS2 transistors with sub-1 nm gate length and sub-50 nm channel length. The channel-all-around geometry and edge-aligned contacts yield on/off ratios up to ~10^6 and on-currents up to ~250 μA/μm at 4 V, representing over 40× improvement versus non-self-aligned controls. The method also enables operation on flexible substrates with minimal performance degradation under strain. Future work should focus on developing scalable self-alignment for vertical structures, reducing total stack thickness while mitigating BN leakage and preserving MoS2 mechanical integrity, optimizing contact metals to minimize Schottky barriers, and improving process yield and manufacturability.

- Process complexity and scalability: The folding and pick-up based self-alignment is intricate and not yet suited for large-scale manufacturing; a scalable vertical self-alignment process is still required.

- Thickness constraints: Thicker stacks (>60 nm) suffer from large strain at the fold causing structural damage and yield loss; thinner stacks (<~30 nm) challenge the self-alignment because metal thickness approaches stack thickness, preventing reliable edge cracking/peeling.

- Material limitations: Monolayer MoS2 is fragile during folding; the thinnest MoS2 used was ~4.5 nm. BN’s relatively low bandgap and dielectric properties lead to increased gate leakage when thinned to a few nanometers, limiting further dielectric scaling.

- Contact asymmetry: Different top (Ti) and bottom (vdW Au) contacts introduce asymmetric Schottky barriers, affecting output symmetry and potentially limiting low-bias performance.

- Yield: While acceptable for research (~77%), yield is not yet at industrial levels.

- Gate leakage modeling: Simulated leakage may underestimate real leakage due to idealized models that do not include defects and interface states.

Related Publications

Explore these studies to deepen your understanding of the subject.