Engineering and Technology

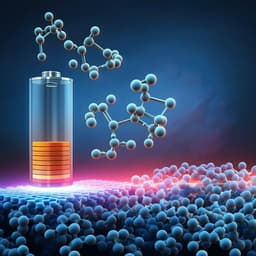

Balancing resistor-based online electrochemical impedance spectroscopy in battery systems: opportunities and limitations

A. Blömeke, H. Zappen, et al.

This groundbreaking study examines the innovative use of existing balancing resistors in battery management systems for online electrochemical impedance spectroscopy measurements. Conducted by a team of experts including Alexander Blömeke and Hendrik Zappen, the research highlights the feasibility, potential strategies for optimization, and the challenges surrounding this novel approach.

Related Publications

Explore these studies to deepen your understanding of the subject.